# **CS2100 Computer Organization**

## AY2024/25 Semester 2 Assignment 2

(Deadline: 17 March 2025, Monday, 1pm)

#### **Instructions**

- 1. There are **5** questions in this assignment, with a total of 40 marks.

- 2. This assignment is due on **Monday, 17 March 2025, 1 pm.** The late submissions will incur penalties: a 10% penalty for submissions up to one day late (e.g., submitting at 10.20pm for a 10pm deadline), a 20% penalty for submissions up to two days late, and no grades will be given for assignments submitted more than two days late.

- 3. Enter your answers into Canvas > Assignment 2.

- 4. Please read and follow the instructions on how to format your answers. This is important as your answers will be autograded, so any answer that departs from the specified format will be graded as incorrect.

- 5. You should do these assignments on your own. Do not discuss the assignment questions with others.

- 6. Please post on QnA "Assignments" topic if you have any queries on this assignment.

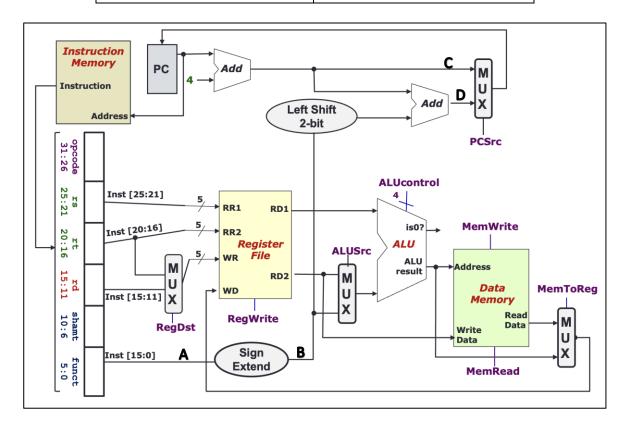

## Part I: MIPS Datapath (20 marks)

### Question 1. (20 marks)

Consider the MIPS Datapath with the initial values of the registers and memory as shown below. Values preceded by 0x are in hexadecimal.

| MIPS Registers                                                 |              |   |            |     |        |              |   |                           |  |  |

|----------------------------------------------------------------|--------------|---|------------|-----|--------|--------------|---|---------------------------|--|--|

| R0 (r0) = $0 \times 000000000$   R1 (at) = $0 \times 00002000$ |              |   |            |     |        |              |   |                           |  |  |

| R2                                                             | (v0)         | = | 0x00000000 |     | R3     | (v1)         | = | 0x000002000               |  |  |

| R4                                                             | (vo)         | = | 0x00000001 |     | R5     | (v1)         | _ | 0x7ffff000                |  |  |

| R6                                                             | (a0)         | = | 0x7ffff004 |     | R7     | (a1)         | = | 0x000000b0                |  |  |

| R8                                                             | (a2)<br>(t0) | = | 0x00000001 |     | R9     | (as)<br>(t1) | = | 0x0000000000000           |  |  |

| R10                                                            | , ,          |   |            |     | R11    |              |   | 0x000000000<br>0xfffffff0 |  |  |

|                                                                | (t2)         | = | 0x0000c000 |     |        | (t3)         | = | *                         |  |  |

| R12                                                            | (t4)         | = | 0xf000000  | -   | R13    | (t5)         | = | 0x00000fff                |  |  |

| R14                                                            | (t6)         | = | 0x00006200 |     | R15    | (t7)         | = | 0x00000e00                |  |  |

| R16                                                            | (s0)         | = | 0x00300000 |     | R17    | (s1)         | = | 0x00000c00                |  |  |

| R18                                                            | (s2)         | = | 0x00040200 |     | R19    | (s3)         | = | 0x00011000                |  |  |

| R20                                                            | (s4)         | = | 0x00030200 |     | R21    | (s5)         | = | 0x0000000                 |  |  |

| R22                                                            | (s6)         | = | 0x00055000 |     | R23    | (s7)         | = | 0xf0000000                |  |  |

| R24                                                            | (t8)         | = | 0x00000005 |     | R25    | (t9)         | = | 0x0000d000                |  |  |

| R26                                                            | (k0)         | = | 0x00000000 |     | R27    | (k1)         | = | 0x0000000                 |  |  |

| R28                                                            | (gp)         | = | 0x10008000 |     | R29    | (sp)         | = | 0x7fffeff4                |  |  |

| R30                                                            | (s8)         | = | 0x1000000f |     | R31    | (ra)         | = | 0x00400018                |  |  |

|                                                                |              |   |            |     |        |              |   |                           |  |  |

| Address                                                        |              |   |            |     | Memory |              |   |                           |  |  |

| 0xffffff94                                                     |              |   |            |     | 100    |              |   |                           |  |  |

| 0xffffff98                                                     |              |   |            |     | 200    |              |   |                           |  |  |

| 0xffffff9C                                                     |              |   |            |     | 300    |              |   |                           |  |  |

| 0xffffffA0                                                     |              |   |            |     | 400    |              |   |                           |  |  |

| 0xFF                                                           | FFFF         |   |            | 500 |        |              |   |                           |  |  |

|                                                                |              |   |            |     |        |              |   |                           |  |  |

Page **2** of **6**

The current PC value and the address of the first instruction is 0x**00001024.** The following instructions are being executed one by one:

```

sw $s6, -100($s5)  # instruction 1

addi $s2, $s3, 0x20  # instruction 2

beq $s6, $s3, target # instruction 3

addi $s4, $s5, 0x40  # instruction 4

target:

```

Fill in the values of the fields in the table below. You have to fill column 2 after executing instruction 1 and column 3 after executing instruction 3. For rows marked with \*, your answers <u>must follow the base given</u> (0b for binary, 0x for hexadecimal), and you must write <u>all the required digits with A to F in capital letters</u>, or it will be graded as wrong even if the value is correct. You do <u>NOT</u> need to include the prefix 0b or 0x in your answers. For rows without \*, the answers are to be in decimal, and you are <u>not</u> to include leading zeroes in your decimal answers. If a control signal is a don't-care value, enter X.

| Fields              | Values after executing<br>Instruction 1 | Values after executing<br>Instruction 3 |  |  |  |  |

|---------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|

| RegDst              |                                         |                                         |  |  |  |  |

| MemRead             |                                         |                                         |  |  |  |  |

| MemWrite            |                                         |                                         |  |  |  |  |

| ALUcontrol*         | 0b                                      | 0b                                      |  |  |  |  |

| RegWrite            |                                         |                                         |  |  |  |  |

| Instruction[31-26]* | 0b                                      | 0b                                      |  |  |  |  |

| Instruction[25-21]* | 0b                                      | 0b                                      |  |  |  |  |

| Instruction[20-16]* | 0b                                      | 0b                                      |  |  |  |  |

| Instruction[15-0]*  | 0x                                      | 0x                                      |  |  |  |  |

| A*                  | 0x                                      | 0x                                      |  |  |  |  |

| B*                  | 0x                                      | 0x                                      |  |  |  |  |

| RD1*                | 0x                                      | 0x                                      |  |  |  |  |

| RD2*                | 0x                                      | 0x                                      |  |  |  |  |

| ALU Result*         | 0x                                      | 0x                                      |  |  |  |  |

| ALUSrc              |                                         |                                         |  |  |  |  |

| RR1                 |                                         |                                         |  |  |  |  |

| RR2                 |                                         |                                         |  |  |  |  |

| MemToReg            |                                         |                                         |  |  |  |  |

| C*                  | 0x                                      | 0x                                      |  |  |  |  |

| D*                  | 0x                                      | 0x                                      |  |  |  |  |

#### Part II. Boolean algebra, logic circuits and simplification (20 marks)

Note that in general, unless otherwise stated, complemented literals are not available. Constants 0 and 1 are always available, and they are considered (degenerated form of) SOP and POS expressions.

Remember to write  $\cdot$  for the AND operation, or mark will be deducted. If you are typing your answers, you may use the full stop (.) for AND and the single quote (') for complement. Do <u>not</u> use other alternative symbols (such as  $\sim A$ ,  $\neg A$ ,  $\bar{A}$ , etc. for the complement of A, write A' instead).

Unless otherwise stated, workings are not required.

The above instructions apply for subsequent assignment, midterm test and the final exam.

Note that no partial credits will be awarded for incorrect answers for most of the questions.

#### Question 2 (Total: 6 marks)

Given a 5-variable Boolean function F(A, B, C, D, E).

- (a) Let x and y be <u>any</u> two distinct integers in the range 0 through 31. What is the result of (minterm x AND minterm y)? (1 mark)

- (b) Pick any two distinct integers x and y and show <u>clearly</u> the working on how you derive your answer for part (a) above. You are to cite the laws/theorems used. (2 marks)

- (c) How many minterms does a 2-literal product term in F have? (1 mark)

- (d) Suppose  $F(A,B,C,D,E) = C \cdot D + A' \cdot C \cdot E + A \cdot D \cdot E$ . Write F(A,B,C,D,E) in the  $\sum m$  notation. You are to list out the minterms in <u>increasing order, enclosed in a pair of parentheses, separated by comma, with no space and no other punctuation</u>. For example, if the answer is  $\sum m$  (3,5,12), you are to enter (3,5,12). No working is needed. (2 marks)

#### Question 3 (Total: 2 marks)

The following Boolean functions F, G, H on 4 variables a, b, c, d are given in sum-of-minterms  $(\sum m)$  notation or product-of-maxterms  $(\prod M)$  notation:

$$F(a, b, c, d) = \sum m(1,2,3,4,5,6,7)$$

$$G(a, b, c, d) = \sum m(0,1,4,5,11,13,15)$$

$$H(a, b, c, d) = \prod M(0,2,4,6,8,11,15)$$

Find (a)  $F' \cdot G$ ; and (b)  $G \oplus H'$ , where  $\oplus$  is the exclusive-or (XOR) operation. Write your answers in the  $\sum m$  notation. You are to list out the minterms in <u>increasing order</u>, enclosed in a pair of parentheses, separated by comma, with no space and no other punctuation. For example, if the answer is  $\sum m$  (3,5,12), you are to enter (3,5,12). No working is needed.

#### Question 4 (Total: 7 marks)

Given the 4-variable Boolean function  $Z(A,B,C,D) = \sum m(1,2,3,7,9,15) + \sum x(0,5,6,11,12)$  where m are the minterms and x are the don't-cares.

- (a) How many prime implicants (PIs) are there on the K-map of Z? [1 mark]

- (b) How many essential prime implicants (EPIs) are there on the K-map of Z? [1 mark]

- (c) How many distinct simplified SOP expressions are there for Z? [1 mark]

- (d) Write out <u>one</u> simplified SOP expression for Z. You are to (1) write the literals with a product term in alphabetical order (eg:  $P \cdot Q' \cdot R$  instead of  $R \cdot Q' \cdot P$  or  $P \cdot R \cdot Q'$ ), and (2) write the essential prime implicants before the non-essential ones. The order among the essential prime implicants and the order among the non-essential prime implicants do not matter. You have to use the dot for AND, plus for OR, single quote for negation, with no space, no unnecessary parentheses and no symbols other than dot, plus, single quote and parentheses. For example, if the answer is  $B \cdot A + C' \cdot D$ , you are to enter A.B+C'.D

- (e) Write out <u>one</u> simplified POS expression for Z. The order of literals in a sum term must be in alphabetical order (eg: U+V'+W' instead of W'+U+V' or U+W'+V'). You have to use the dot for AND, plus for OR, single quote for negation, with no space, no unnecessary parentheses and no symbols other than dot, plus, single quote and parentheses. For example, if the answer is  $(B+A)\cdot(C'+D)$ , you are to enter (A+B).(C'+D)

#### **Question 5** (Total: 5 marks)

The 2421 code for the ten decimal digits 0 to 9 is shown in the table below:

| Decimal digit | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---------------|------|------|------|------|------|------|------|------|------|------|

| 2421 code     | 0000 | 0001 | 0010 | 0011 | 0100 | 1011 | 1100 | 1101 | 1110 | 1111 |

Parity bit is an error-detection scheme. In the even parity bit scheme, the parity bit is assigned 0 if the number of 1's in the data bits is an even number, or assigned 1 if the number of 1's in the data bits is an odd number.

You are to design a circuit that takes in a 4-bit 2421 code *ABCD* and generates two outputs *V* and *P*: output *V* is 1 if the input is a valid 2421 code, or 0 otherwise; output *P* is the parity bit.

For simplified SOP expressions, you are to (1) write the literals with a product term in alphabetical order (eg:  $P \cdot Q' \cdot R$  instead of  $R \cdot Q' \cdot P$  or  $P \cdot R \cdot Q'$ ), and (2) write the essential prime implicants before the non-essential ones. The order among the essential prime implicants and the order among the non-essential prime implicants do not matter. You have to use the dot for AND, plus for OR, single quote for negation, with no space, no unnecessary parentheses and no symbols other than dot, plus, single quote and parentheses.

(a) How many simplified SOP expressions are there for *V*?

[1 mark]

(b) Write out one simplified SOP expression for V.

[1 mark]

(c) Write out the simplified SOP expression for P.

[2 marks]

(d) Write an alternative expression for *P* which can be implemented with at most 3 logic gates. (Logic gates allowed are inverters, AND, OR, NAND, NOR, XOR and XNOR. Except for inverters, all logic gates are 2-input gates.) Use dot for AND, plus for OR and single quote for negation. Type the words NAND, NOR, XOR and XNOR if they used, for example: (A NOR B)+(C NAND D). You may type a space before and after the words NAND, NOR, XOR and XNOR, but there should be no space in the rest of your answer.

=== END OF PAPER ===